关键词 > EEC180

EEC180 — DIGITAL SYSTEMS II WINTER QUARTER — 2023 FINAL EXAM

发布时间:2024-06-12

Hello, dear friend, you can consult us at any time if you have any questions, add WeChat: daixieit

EEC180 — DIGITAL SYSTEMS II

WINTER QUARTER — 2023 — 5 UNITS

FINAL EXAM

1. IEEE 754 STANDARD (25 POINTS)

Consider the two numbers A = 4.0 and B = -2.5. We would like to use the IEEE 754 standard representation. In this problem, we assume a 16-bit representation with 1 bit for sign, 5 for expo- nent in excess-15 notation (means the bias is 15), and 10 bits for the mantissa.

1. What is the minimum positive number that can be represented if the significand is normalized? (4 points)

2. What is the maximum positive number that can be represented? (4 points)

3. What decimal number is represented by the bit pattern 1000000000000111? (4 points)

4. Find the IEEE 754 binary representation of the numbers A and B. (5 points)

5. Compute P = A × B using the binary (not decimal) floating-point representations of A and B. (8 points)

2. MEMORY DESIGN (25 POINTS)

Suppose that we have the following memory chips:

M1: 128K × 2 M2: 128K × 2 M3: 128K × 4

M4: 128K × 8 M5: 256K × 2 M6: 256K × 2

M7: 256K × 4

Each of the above memory chips comes with tri-state bidirectional data input/output connec- tions. You can assume that each chip has the following ports: address a, data d, enable en, and write wr. Note that if wr = 0, the chip works in a read mode.

We would like to build a memory system 2m × n using all of the above chips. All chips must be completely utilized.

1. What are the possible values of m? For each value of m, find the corresponding value of n. (10 points)

2. If n = 8, show a complete diagram (including the decoding logic) for the memory system. (15 points)

3. COUNTERS (25 POINTS)

Consider a 5-bit binary counter with the following specifications:

• The counter has a clock input as well as a synchronous input reset. It also has a count out- put.

• The counting sequence of the counter is as follows: 0, 17, 2, 19, 4, 21, 6, 23, 8, 25, 10, 27, 12, 29, 14, 31, and repeat.

• The counter resets (count = 0) when reset = 1.

Write a Verilog model for the counter that should not be more than 10 lines of code.

4. FSM IMPLEMENTATION (25 POINTS)

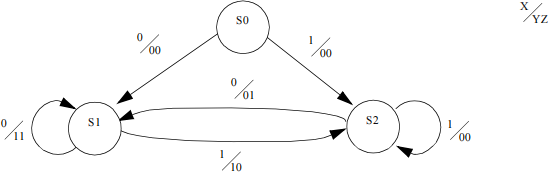

A Mealy finite state machine (FSM) has one data input x and two outputs y and z. The output y = 1 occurs when 00 or 01 is observed on the input x. The output z = 1 occurs when 00 or 10 is observed on the input x. The finite state machine also has a synchronous input reset. When reset = 1 , the next state in the FSM will be state S0 independent of the value of x. The state dia- gram of this machine (without showing the reset input) using the minimum number of states is shown below.

1. Write a behavioral verilog model of the finite state machine. (7 points)

2. Design a circuit (with inputs x and reset, and outputs y and z) that implements the above state diagram and uses one-hot encoding for the state assignment. Assume that the only available components are D flipflops (with Q output) and 2-input NOR gates. Make sure to use the minimum number of NOR gates. (7 points)

3. Write a verilog model for a D flip-flop (with Q output). (2 points)

4. Write a verilog model for a 2-input NOR gate. (2 points)

5. Write a structural verilog model of your design in part 2 using the components described in parts 2 and 3. (7 points)

5. FPGA IMPLEMENTATIONS (25 POINTS)

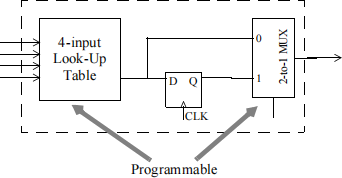

Assume that we have an FPGA with a simple Configurable Logic Blocks (CLBs). Each CLB in the FPGA has one output that can implement any function with 4 variables using a 4-input look-Up Table. The diagram of the CLB is shown below:

In the parts below, assume that we can always route the signals successfully among the CLBs.

1. What is the minimum number of CLBs needed to implement any function with 5 variables? (5 points)

2. What is the minimum number of CLBs needed to implement any function with 6 variables? (5 points)

3. What is the minimum number of CLBs needed to implement a 4-bit ripple carry adder? (5 points)

4. What is the minimum number of CLBs needed to implement an 8-to-1 multiplexor? (5 points)

5. What is the minimum number of CLBs needed to implement an 16-to-1 multiplexor? (5 points)