关键词 > EEC180

EEC 180 — DIGITAL SYSTEMS II SPRING QUARTER — 2024 MIDTERM EXAM

发布时间:2024-06-11

Hello, dear friend, you can consult us at any time if you have any questions, add WeChat: daixieit

EEC 180 — DIGITAL SYSTEMS II

SPRING QUARTER — 2024

MIDTERM EXAM

1 COUNTERS (25 POINTS)

Consider an 8-bit counter with the following specifications:

• The counter has two synchronous inputs RESET and M.

• If RESET = 1, the counter resets the state to 00000000. Otherwise, the state is updated according to the value of M.

• If M = 0, the counter counts up.

• If M = 1, the counter t toggles the four most significant bits of its state. For example, if the counter state is 01101101 and M = 1, then the next state is 10011101.

Write a Verilog model for the counter. Assume that it is the responsibility of the user of the counter to reset it before using it.

2 RANGE DETECTOR (25 POINTS)

Develop a Verilog model for a range detector that finds the difference between the maximum and minimum values in a sequence of 6-bit unsigned integers. A new number arrives at the input data_in during a clock cycle when the data_en input is 1. Once the new number is arrived, the data_out output need to be updated. The data_out output is cleared to zero when the reset control input is 1. Both data_en and reset are synchronous control inputs.

3 VERILOG CODING (15 + 10 = 25 POINTS)

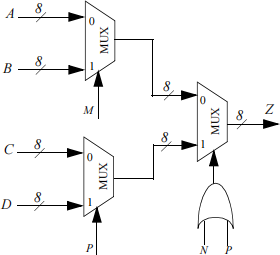

Consider the implementation shown below.

1. Develop a Verilog structural model for the above circuit. A structural model is based on instantiations of basic modules.

2. Develop a Verilog model for the above circuit using a single assign statement.

4 COMBINATIONAL ARITHMETIC CIRCUITS (15 + 10 = 25 POINTS)

Consider a combinational circuit that computes the arithmetic function Z = X2 + 2X + 3, where X is an n-bit unsigned number and Z is a 2n-bit unsigned number. The circuit also produces an overflow output ovf that indicates if an overflow is obtained.

1. How many X values will cause an overflow?

2. Write a verilog model for the above circuit for the case of n = 5.

5 FINITE STATE MACHINES (25 POINTS)

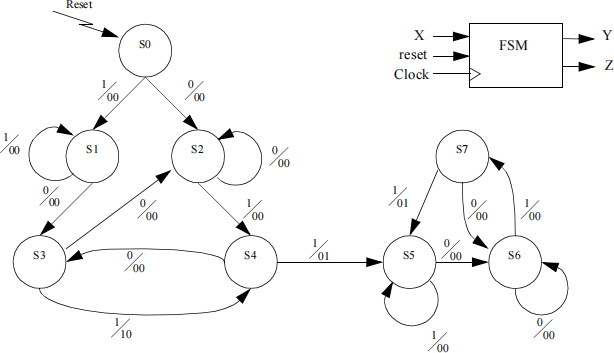

Write a Verilog model for the finite state machine with the state diagram shown below.