关键词 > ECE4535/6005

ECE 4535/6005 Computer Architecture & Design

发布时间:2021-11-25

Hello, dear friend, you can consult us at any time if you have any questions, add WeChat: daixieit

ECE 4535/6005 Computer Architecture & Design

Fall 2021

Lab Assignment #4

Instructions:

Submit one report (preferably pdf format). In the report, please include the code segments that you have modified in source or configuration files, and the commands that you have used for simulation. Please try to use figures or tables to present your results and provide the necessary analysis.

Problem 1: Gem5 Python Script (20 × 2 = 40)

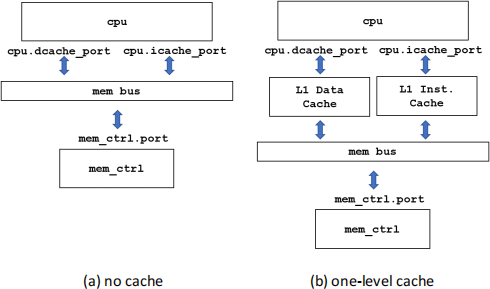

Compare the performance of the two architectures listed below using the provided test program in the Gem5 simulator. You can use the system emulation (SE) mode and assume a timing simple CPU working at 1 GHz and a 512 MB DDR3 main memory. Show the Python configuration files for three architectures separately and report the key simulation results (e.g. execution time, cache hit rate, etc.).

a) The CPU is connected to the main memory through a bus

b) The CPU is connected to the level-one instruction/data caches and then to the main memory through a bus. Both L1 instruction cache and L1 data cache share the same parameters: 1 kB size, direct-mapped, 2-cycle tag latency, 2-cycle data latency, and 2-cycle response latency. You can use default values for other parameters or of your choice.

Hints:

1. Download the test program using wget command from the following link: https://github.com/gwuyuan/lab-assignment-3/raw/main/test. This test program performs arithmetic operations on large 2D arrays.

2. Use SystemXBar and L2XBar Python classes for connections of main memory and L2 cache (if necessary), respectively.

Problem 2: Gem5 SE Simulation (10 × 3 = 30)

Explore the impact of cache organization on system performance. Adopt the Python configuration file in Problem 1 (b) and report the cache hit rate and execution time.

a) Vary the cache capacity (1 kB, 4 kB, 16 kB, and 32 kB) and report the simulation results. Other cache parameters remain the same as in Problem 1 (b).

b) Vary the cache associativity (direct-mapped, 4-way, 8-way, and fully associative) and report the simulation results. Other cache parameters remain the same as in Problem 1 (b).

c) The tag latency is often related to cache associativity. For example, the direct-mapped cache has low tag latency while the fully associative cache has relatively higher tag latency. Assume that the tag latency values for direct-mapped, 4-way, 8-way, and fully associative cache are 2 cycles, 5 cycles, 10 cycles, and 20 cycles, respectively. Report the simulation results and conclusions that you can draw. Other cache parameters remain the same as in Problem 1 (b).

Hints:

1. You can use the application from Problem 1 or compile other C/C++ source files of your choice using the default gcc/g++ compilers in the system for simulation.

2. Use bash script as we have done in Dinero IV and SimpleScalar simulators.

Problem 3: Gem5 Python Class Interface (15 × 2 = 30)

The following table lists the configuration parameters of two architectures. The first architecture includes a small core with low operating frequency, limited compute capability, and a small cache footprint. The second architecture includes a large core with high operating frequency, high compute capability, and a large cache footprint. Compare the performance of these architectures in Gem5.

a) Report the configuration command for each of the two architectures and other necessary modifications you have done in Python class definitions.

b) Report the performance (execution time) comparison of these two architectures.

Hints:

1. You can use the application from Problem 1 or compile other C/C++ source files of your choice using the default gcc/g++ compilers in the system for simulation.

2. You may need to use the script provided by the simulator at: ~/gem5/configs/example/se.py.

3. Some of the parameters listed in the table can be configured using options provided by the se.py file while other parameters need to be configured in the original Python class definition files which are located in: ~/gem5/src/cpu/.