ELE00026C Digital Systems Coursework Assessment 2020/21

Department of Electronic Engineering

ELE00026C Digital Systems Coursework Assessment 2020/21

SUMMARY DETAILS

This coursework (Individual Report) contributes 30% of the assessment for this module.

Clearly indicate your Exam Number on every separate piece of work submitted.

Submission is via the VLE module submission point. The deadline is 12:00 on 11/5/2021, Summer Term, Week 4, Tuesday. Please try and submit early as any late submissions will be penalised. Assessment information including on late penalties is given in the Statement of Assessment.

ACADEMIC INTEGRITY

It is your responsibility to ensure that you understand and comply with the University’s policy on academic integrity. If this is your first year of study at the University then you also need to complete the mandatory Academic Integrity Tutorial. Further information is available at http://www.york.ac.uk/integrity/.

In particular please note:

● Unless the coursework specifies a group submission, you should assume that all submissions are individual and should therefore be your own work.

● All assessment submissions are subject to the Department’s policy on plagiarism and, wherever possible, will be checked by the Department using Turnitin software.

Digital Systems Assignment 2020/21

Dr Martin Trefzer

1. Task

This assessment is about interrupts. You are required to design a modification to the CPU you worked on in the Spring term to add an interrupt request input, and to write a short report about interrupts and interrupt handling in general, and your modifications in particular.

2. Report details

You must write a report that is no longer than 2000 words in length. Your report must contain, in order:

2.1 An introduction to interrupts [20 marks]

Describe what an interrupt request is, and what the CPU does when the request arrives. What are interrupts useful for? Make sure you define the terms ‘interrupt request’, ‘interrupt vector’, and ‘interrupt service routine’. What does the priority of an interrupt mean?

2.2 A short description of the interrupt handling mechanism on the STMicroelectronics STM32 Nucleo-64 MCU Development Board [20 Marks].

The STM Nucleo-64 MCU board features an ARM Cortex-M4 microcontroller. You can find information on interrupts of the STM Nucleo-64 board in the datasheet (stm32f303re.pdf, also available on the VLE), and information on the ARM Cortex-M4 in the user guide (DUI0553A_cortex_m4_dgug.pdf, also available on the VLE). Look at the sections explaining interrupts and the Nested Vectored Interrupt Controller.

● How many interrupt sources does the STM Nucleo-64 have?

● Are the priorities configurable?

● Do interrupt service routines nest?

● Describe the sequence of events that take place when an interrupt request arrives, if you can explain how the Cortex-M4 NVIC’s registers are affected, so much the better. You may find the information from the Cortex-M4 user guide in section 4.2 useful.

2.3 A design of a basic Interrupt Controller (IC) to suit the simple processor you developed in the Spring term laboratory sessions.

The specifications for the problem:

● Upon receiving an interrupt request (IRQ) the controller should complete the current instruction. It should then store the current program counter (PC) value+1, and force the PC to 10000b, which is the interrupt vector. Further interrupts are inhibited until the end of the interrupt service routine (ISR), at which point the PC is restored.

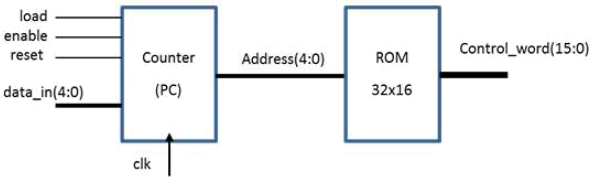

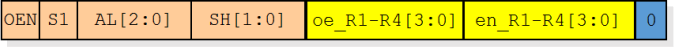

● To keep the design simple, you are only required modifying the Control Unit of the simple processor to include an interrupt controller. Figure 1 gives a good starting point for the Control Unit which contains a 5-bit counter (acts as the PC) and the ROM that stores 16-bit control words for the data path. The control word has the bit allocations as shown in figure 2 and this is the same as the format you used in the spring term labs. The least significant bit which we didn’t use in the lab exercises is available for you to use in this design.

Figure 1. A starting point for the Control Unit: A counter with synchronous load (that loads the values on data_in(4:0) and a 32x16 ROM. Control signals have their usual meaning.

Figure 2. Control word.

● You may find a register, an adder, and a 2-to-1 multiplexer (all work with 5-bits wide data) useful in the design and you may assume those building blocks are readily available for you to use. While you may not require any other building blocks you are allowed to add any other building blocks demanded by your design.

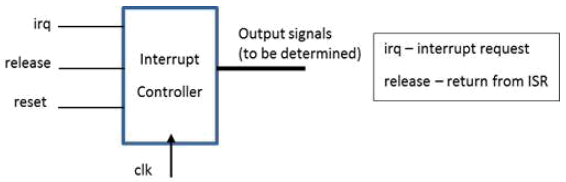

● Figure 3 shows the external view of the interrupt controller that will be added to the control unit. The inputs to the interrupt controller are IRQ, release and reset. You are expected to determine the number of output signals, what they are for, and where those outputs signals will be connected in your design. The outputs of the interrupt controller are generated in a certain order to handle an interrupt (see the very first point above), thus can be realised with a finite state machine (FSM). In other words, interrupt controller can be realised with a finite state machine. You may use either a Moore or a Mealy FSM model to design your interrupt controller, however, a Mealy FSM is more appropriate in this application.

Figure 3. The external view of the Interrupt Controller.

● There is no requirement for you to write the control words for the interrupt service routine, but you should consider the control word for the ‘return from the interrupt service routine’.

● You may find work done and knowledge accumulated in spring term labs, specially from lab scripts 3-6 useful in this design.

● Note that there is no requirement for you to simulate, synthesise or implement your design using Xilinx tools as this is limited to a design task.

To validate your design, you should include the following in the report in the order specified below [40 Marks]:

● A clearly labelled block diagram of the Control Unit with a short description of the modifications required for the Control Unit.

● A clearly labelled state transition diagram of the FSM for the Interrupt Controller with brief but clear statements of what each state does. There is no requirement for you to show the other steps of the FSM design.

● The control word for the ‘return from the interrupt service routine (ISR)’ to fit your design.

● A simple timing diagram with relevant signals, PC, and the content of the register you added to the design to illustrate the important events like the entry to and return from the ISR. It is up to you to decide which signals are relevant to illustrate the functionality of your design.

Some guidelines on your report and the marking scheme are given on the next page.

3. Some guidelines on your report

Academic conduct

This is an individual submission. You are welcome to consult any sources of information you can find as long as you provide appropriate reference and attribution to the authors.

If the rules on what constitutes correct academic conduct are not clear, please consult section 5.7 of the university rules and regulations here: 5.7 Academic misconduct. The department guidance on plagiarism can also be found here: Transferable Skills web page.

Report submission

The report should be submitted as a PDF file, containing all the material required in the order specified. Report submission will be electronic via the VLE. Please read carefully the instructions on the VLE submission page. Failure to follow the instructions could lead to your assignment not being marked or a mark penalty.

Report layout and format

There is no formal report structure, but your report should include a short introduction, an outline to the report, technical content outlined in section 2 (in the specified order), a summary or conclusion and a list of references. You are expected to use a suitable software tool to generate any relevant diagram for this assignment

You can find general guidelines on report writing on the departmental Transferable Skills web page. We recommend that you use: 12pt Calibri font with single line spacing, 1 cm margins and IEEE referencing style (all relevant details in the above link).

Marking Scheme

● 20% - general layout of the report and presentation; introduction, summary/conclusion, and referencing

● 80% - technical merit as outlined in section 2

2021-04-07