ECE363 Computer-Aided Design of Digital Systems Homework 2

Hello, dear friend, you can consult us at any time if you have any questions, add WeChat: daixieit

Homework 2

ECE363 Computer-Aided Design of Digital Systems

Please submit your answer with a single PDF via the course site.

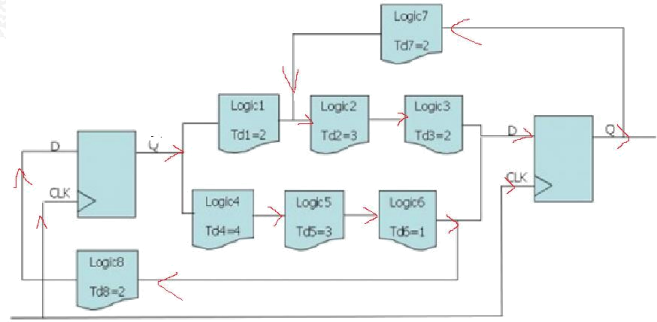

Q1: Assume clock cycle is 20ns, cell delay of each register is 0.5ns, the setup and hold time of each register are 1ns and 0.5ns, respectively.

1) How many different timing paths in the following logic? Mark it in the figures.

2) Calculate the delays of each marked timing path.

3) What are the longest and shortest paths?

4) What are the timing slacks for setup and hold time?

Q2: Assume clock cycle is 9ns, cell delay of each register is 1ns, the setup of each register is 1ns.

1) Calculate the setup time slack of the Path 1 and Path 2.

2) Do path 1 and path 2 satisfy the setup timing requirement? If not, which path can /cannot meet the timing?

3) Can you figure out a simple way to fix the timing issues in those two paths: Make sure the timing slacks for path 1 and path 2 are both +0.5ns? (Hint, tune one of the clock delay)

2023-05-12